V predchádzajúcom článku sme predstavili vývojovú dosku pre FPGA ALTERA Cyclon IV a inštaláciu vývojového prostredia Quartus II. Field Programmable Gate Array, čiže po našom programovateľné logické pole má široké možnosti uplatnenia a veľa režimov programovania. V článku ukážeme príklad jednoduchej aplikáciu typu blinky, pomocou ktorej rozblikáme dve LED na vývojovej doske.

Video ukazuje postup naprogramovania jednoduchej aplikácie pre FPGA Cyclon IV

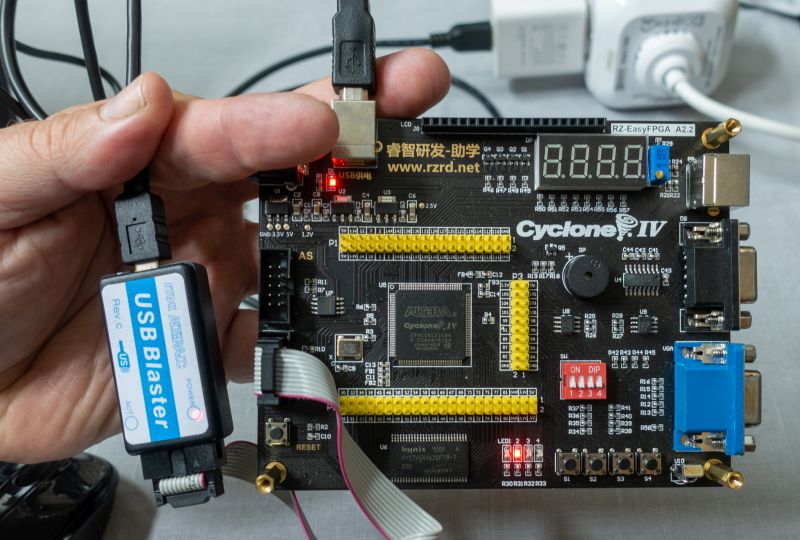

Komponenty na vývojovej doske

Primárnym cieľom takéhoto príkladu je uistiť sa, že máte správna nainštalované a nakonfigurované vývojárske nástroje a správne pripojené zariadenie, na ktorom aplikáciu testujete. Cieľom aplikácie je striedavo blikať dvomi LED diódami v takte 1 Hz. Technicky povedané striedavo nastavovať na príslušných pinoch, ku ktorým sú diódy pripojené úrovne „logická 0“ a „logická1“.

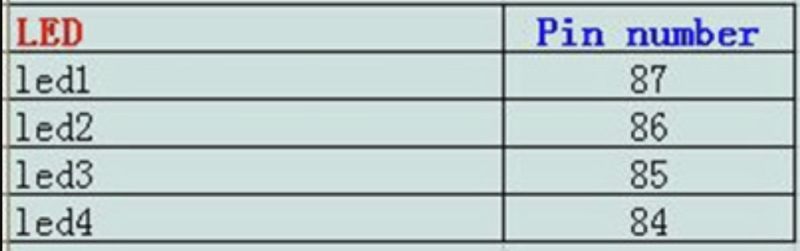

Aby sme mohli blikať LED-kami na doske, potrebujeme vedieť na ktoré piny sú LED na doske pripojené. Zistíme to z tabuľky

Táto vývojová doska má síce aj štvormiestny 7 segmentový displej, takže by sme mohli zobrazovať aj inkrementálne počítadlo, prípadne zjednodušené hodiny, avšak našim cieľom bolo aby prvý príklad bol čo najjednoduchší a niečo si treba nechať aj na prípadný ďalší diel.

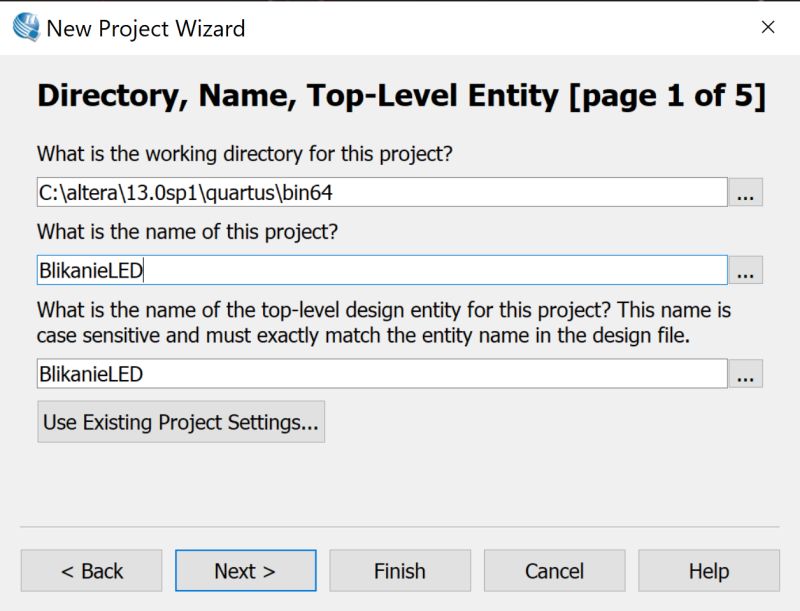

Vytvorenie projektu

Po spustení vývojového prostredia Quartus II vytvoríme nový projekt pre konkrétne FPGA. Zadáme názov projektu. Vývojové prostredie nám automaticky ponúkne zložku pre ukladanie súborov nového projektu.

V nasledujúcom dialógu vyberieme typ FPGA. Najskôr vyberieme produktovú rodinu, v našom prípade Cyclone IV E a následne konkrétny čip, v našom prípade EP4CE6E22C8

Nakoľko je to prvý projekt takže logicky nemáme do neho čo pridať. Pri ďalších projektoch môžete ak sa to hodí pridať súbory z predchádzajúcich projektov. Rovnako aj v dialógu EDA Tool Settings zatiaľ nemáme žiadne nástroje na simuláciu ani syntézu. Takže sa posunieme ďalej a zobrazia sa nám sumárne informácie o projekte.

Budeme programovať v jazyku VHDL, ak chceme dešifrovať túto skratku tak ju najskôr uvedieme úplnú, čiže VHSIC-HDL (Very High Speed Integrated Circuit Hardware Description Language).

Do projektu preto pridáme súbor typu VHDL File zo zložky Design Files. Do takto vytvoreného súboru môžeme začať písať kód.

Najskôr je potrebné pripojiť knižnice a následne vytvoríme entitu,, nazvime ju napríklad blinky_led v ktorej priradíme generátor taktovacej frekvencie od ktorého odvodíme frekvenciu blikania a priradíme porty na ktorých sú pripojené LED diódy na doske.

Následne pre túto entitu vytvoríme architektúru, kde sú definované konštanty a premenné. Aplikačná logika bude v bloku ohraničenom kľúčovými slovami begin a end. Vytvoríme čítač, v ktorom budeme počítať nábežné hrany signálu. Nakoľko máme frekvenciu kryštálu 50 MHz

constant XTAL_FRQ : integer := 50000000;

a LED chceme blikať s frekvenciou 1 Hz, stačilo by nám napočítať 50 000 000 /2 nábežných hrán. Aby sme nemuseli laborovať s kódom ak by sme LED-kami chceli blikať rýchlejšie,a lebo pomalšie, zadefinujeme frekvenciu blikania

constant LED_FRQ : integer := 1;

A počet nábežných hrán vypočítame:

constant MAX_CNT : integer := ((XTAL_FRQ/LED_FRQ)/2);

V bloku kódu pri nábežnej hrane inkrementujeme stavovú premennú čítača a testujeme, či sme nenapočítali potrebný počet taktovacích cyklov a ak áno, zmeníme stavovú premennú.

process(clk) begin if rising_edge(clk) then --nabežná hrana if (cnt = MAX_CNT) then --maximum? cnt <= (others => '0'); stav_LED <= not stav_LED; else cnt <= cnt + 1; end if; end if; end process;

Podľa tejto stavovej premennej aktualizujeme stav na pinoch na ktorých sú LED diódy. Stav druhej LED bude negáciou stavovej premennej.

led1 <= stav_LED; led2 <= not stav_LED;

Kompletný kód bude:

-- knižnice library ieee; use ieee.std_logic_1164. all; use ieee.numeric_std.all; -- entita entity BlikanieLED is port ( clk : in std_logic; led1 : out std_logic; led2 : out std_logic ); end BlikanieLED; -- architektura architecture rtl of BlikanieLED is signal stav_LED : std_logic; -- definície konštánt constant XTAL_FRQ : integer := 50000000; constant LED_FRQ : integer := 1; -- koľko hrán má napočítať čítač constant MAX_CNT : integer := ((XTAL_FRQ/LED_FRQ)/2); signal cnt : unsigned(24 downto 0); -- aktualny stav čítača begin process(clk) begin if rising_edge(clk) then --nabežná hrana if (cnt = MAX_CNT) then --maximum? cnt <= (others => '0'); stav_LED <= not stav_LED; else cnt <= cnt + 1; end if; end if; end process; led1 <= stav_LED; led2 <= not stav_LED; end rtl;

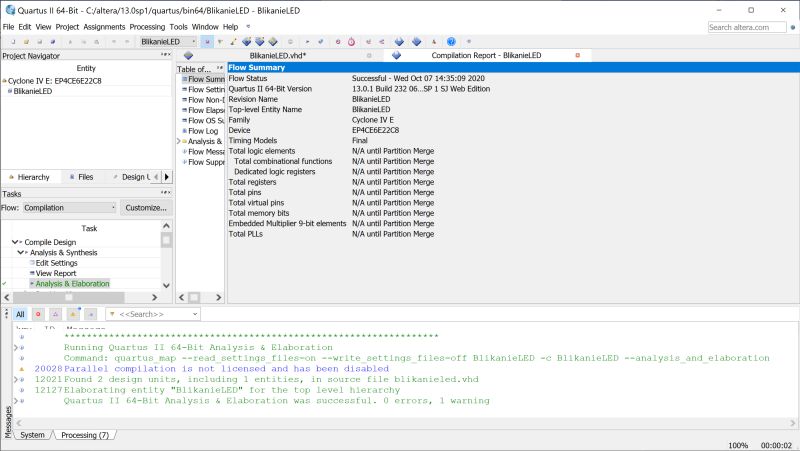

Po napísaní kódu môžete pomocou voľby Analysis&Elaboration skontrolovať jeho syntaktickú správnosť. Prípadné chyby samozrejme opravte. Ak je všetko v poriadku, môžete pokračovať.

Určite vás napadlo, že sme deklarovali porty led1 a led 2, avšak nepriradili sme im piny FPGA čipu. Pre našu vývojovú dosku je led1 pripojená na pin 87 a led 2 na pin 86. Viď tabuľku

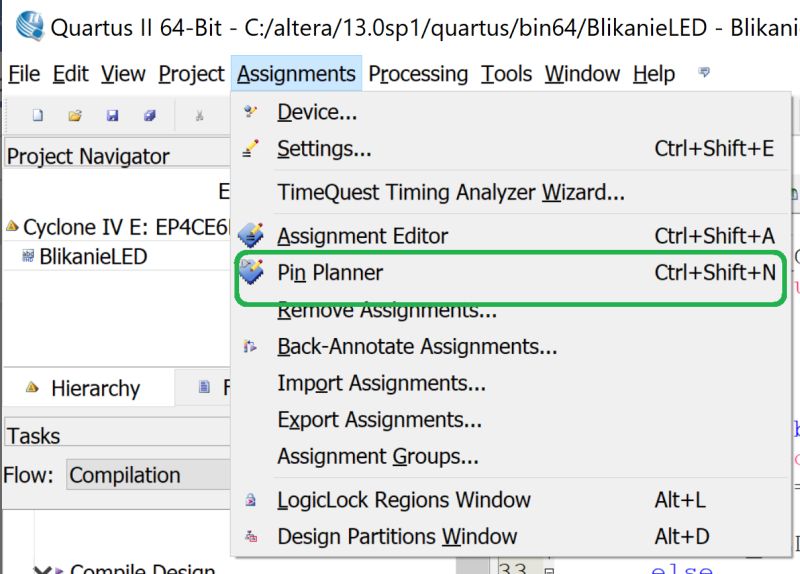

Vo vývojovom prostredí aktivujte v menu voľbu Assignments -> Pin Planner.

Zobrazí sa nám čip so všetkými nožičkami. Nás bude zaujímať tabuľka v spodnej časti, kde sú nami priradené porty clk, led1 a led2. Priradíme im zodpovedajúce piny: clk pripojíme na PIN_23, led1 na PIN_87 a led2 na PIN_86.

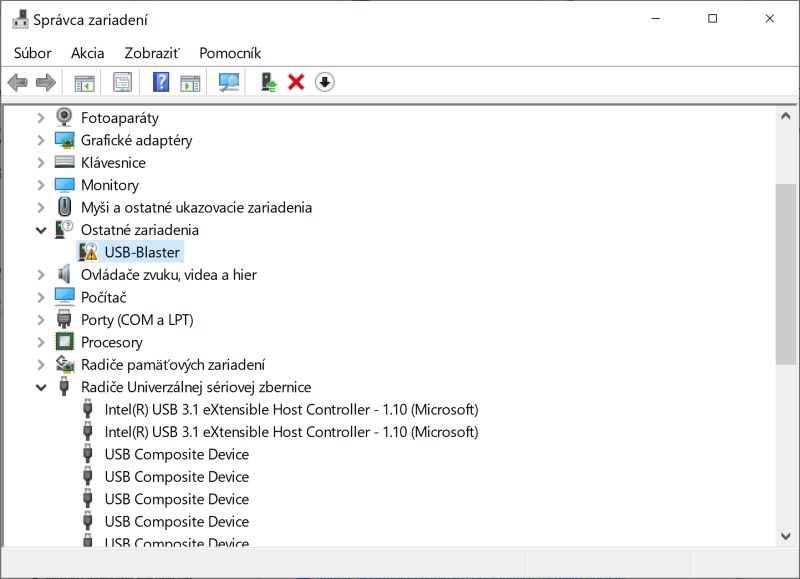

Po priradení pinov máme všetko pripravené na zavedenie programovej logiky do FPGA. Vývojovú dosku pripojíme cez USB konektor typu B (hrubší štvorcového tvaru – aký sa používa na tlačiarni) k napájaciemu zdroju. Ja som použil ako zdroj nabíjačku od schopnú dodať 5V 2A. Pomocou káblika pripojíme modul USB Blaster do konektora na doske označeného JTAG. USB Blaster cez konektor pripojíme k PC. Možno bude potrebné upresniť ovládač.

Pomocou klávesovej skratky Windows+X zobrazte menu a v ňom vyberte položku Správca zariadení. Zobrazí sa zariadenie USB Blaster a pri aktualizácii ovládača zadajte cestu C:\altera\13.0sp1\quartus\drivers (platí pre môj konkrétny prípad keď mám nainštalovanú webovú verziu Quartus II 13.0 Service Pack1).

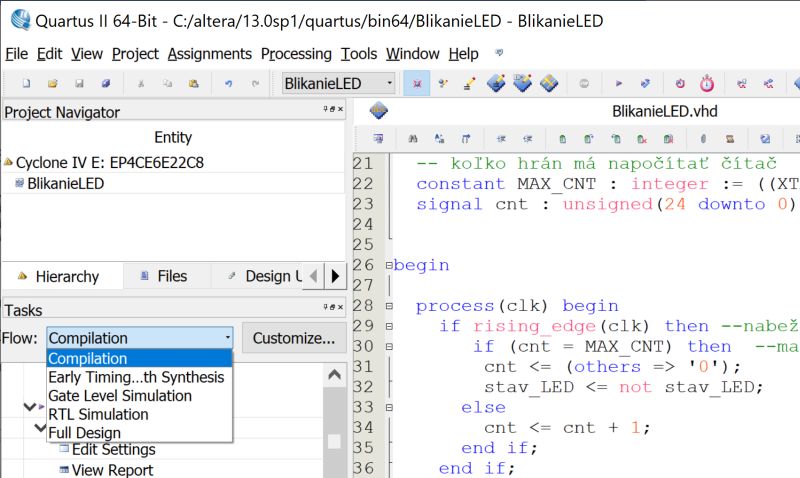

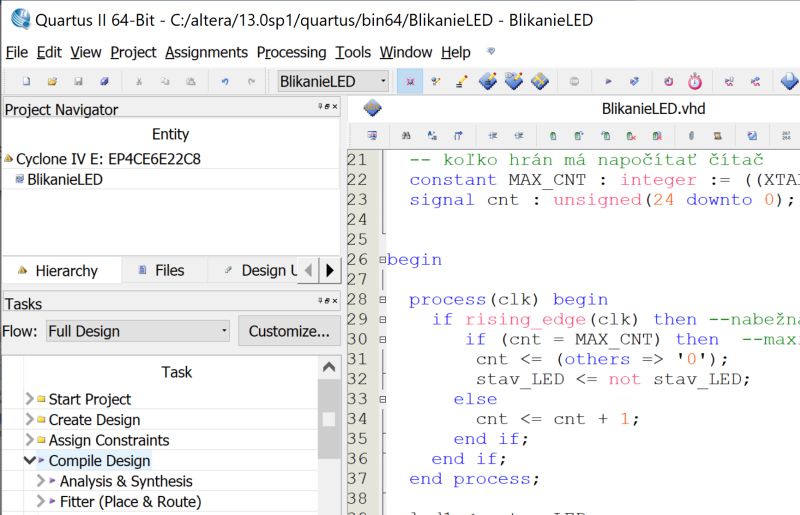

Takže ideme urobiť finálnu kompiláciu programu a zaviesť ho do vývojovej dosky. Vo vývojovom prostredí prepnite v dolnej časti ľavého okna voľbu flow na Full design.

Následne aktivujte voľbu Compile Design.

Zobrazí sa výsledok kompilácie

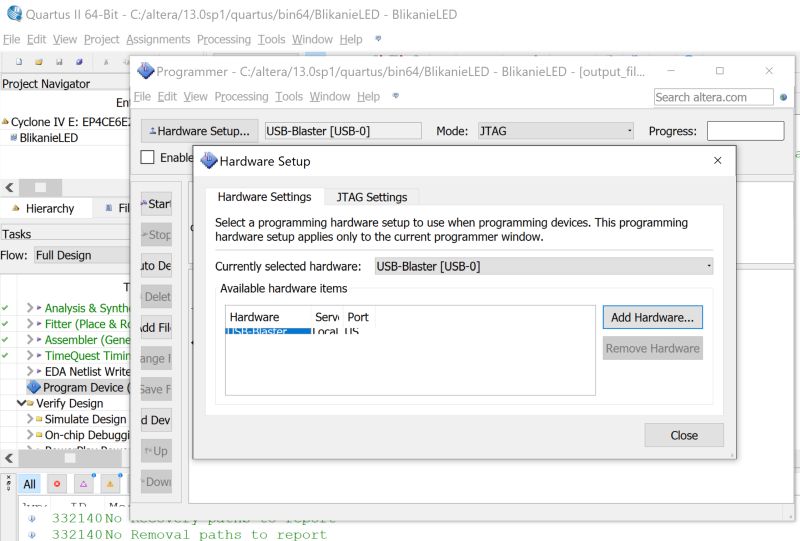

Po úspešnej kompilácii aktivujte voľbu Program Device na zavedenie programu do čipu na vývojovej doske. V dialógu kliknite na Hardware Setup .

Zo jednopoložkového zoznamu vyberte USB Blaster. Skontrolujte či je priradený súbor s kompilovaným programom. Má príponu .sof. Ak nie tak tento súbor vyhľadajte a pomocou voľby Add File priradte. V mojom prípade sa jednalo o súbor BlikanieLED.sof v adresári C:\altera\13.0sp1\quartus\bin64\output_files. Následne tlačidlom Start nahrajte program do dosky.

Ak je všetko v poriadku, mali by v striedavom rytme blikať diódy LED1 a LED2

Převzato ze stránky Nextech se souhlasem autora